# » Kontron User's Guide«

### AM4211

Document Revision 1.0 May 2012

## **Revision History**

| Rev. Index | Brief Description of Changes | Date of Issue |

|------------|------------------------------|---------------|

| 1.0        | First Release                | May 2012      |

|            |                              |               |

|            |                              |               |

## **Customer Service**

Contact Information:

Kontron Canada, Inc.

4555 Ambroise-Lafortune Boisbriand, Québec, Canada

J7H 0A4

Tel: (450) 437-5682

(800) 354-4223 Fax: (450) 437-8053

E-mail: support@ca.kontron.com

**Kontron Modular Computer GMBH**

Sudetenstrasse 7 87600 Kaufbeuren

Germany

+49 (0) 8341 803 333

+49 (0) 8341 803 339

Support@kontron-modular.com

Visit our site at: www.kontron.com

© 2011 Kontron, an International Corporation. All rights reserved.

The information in this user's guide is provided for reference only. Kontron does not assume any liability arising out of the application or use of the information or products described herein. This user's guide may contain or reference information and products protected by copyrights or patents and does not convey any license under the patent rights of Kontron, nor the rights of others.

Kontron is a registered trademark of Kontron. All trademarks, registered trademarks, and trade names used in this user's guide are the property of their respective owners. All rights reserved. Printed in Canada. This user's guide contains information proprietary to Kontron. Customers may reprint and use this user's guide in other publications. Customers may alter this user's guide and publish it only after they remove the Kontron name, cover, and logo.

Kontron reserves the right to make changes without notice in product or component design as warranted by evolution in user needs or progress in engineering or manufacturing technology. Changes that affect the operation of the unit will be documented in the next revision of this user's quide.

## **Table of Contents**

|    | Sa   | afety Instructions                | vii  |

|----|------|-----------------------------------|------|

|    | Ве   | efore You Begin                   | .vii |

|    | Pr   | reventing Electrostatic Discharge | viii |

|    | Sa   | afety Requirements                | . ix |

|    | Pr   | reface                            | . x  |

|    |      | How to Use This Guide             | x    |

|    | Cu   | ustomer Comments                  | x    |

|    | Ac   | dvisory Conventions               | . xi |

|    | Ur   | npacking                          | xii  |

|    | Re   | egulatory Compliance Statements   | xiii |

|    | Li   | mited Warranty                    | xiv  |

| 1. | Pr   | roduct Description                | . 2  |

|    | 1.1  | Product Overview                  | . 2  |

|    | 1.2  | What's Included                   | . 3  |

|    | 1.3  | Board Specifications              | . 3  |

|    | 1.4  | Hot Swap Capability               | . 4  |

|    | 1.5  | Software Support                  | . 5  |

| 2. | В    | oard Features                     | . 7  |

|    | 2.1  | Block Diagram                     | . 7  |

|    | 2.2  | System Core                       | . 8  |

|    | 2.   | .2.1 Cavium OCTEON II CN6645      | 8    |

|    | 2.3  | eUSB Storage                      | . 9  |

|    | 2.4  | SFP+ Front IO                     | 10   |

|    | 2.5  | Gigabit Ethernet                  | 10   |

|    | 2.6  | Serial Rapid I/O (SRIO)           | 11   |

|    | 2.7  | PCIe                              | 11   |

|    | 2.8  | SGMII / XAUI                      | 12   |

|    | 2.9  | RS232 Management Interface        | 12   |

|    | 2.10 | IPMI                              | 12   |

|    | 2.11 | AMC Connector                     | 13   |

|    | 2.12 Front | t Panel LEDs                             | 14 |

|----|------------|------------------------------------------|----|

|    | 2.12.1     | Hot Swap LED (Blue LED)                  | 14 |

|    | 2.12.2     | Out-Of-Service (OOS) LED (LED1)          | 14 |

|    | 2.12.3     | Health LED (LED2)                        | 15 |

|    | 2.12.4     | SFP + LED                                | 15 |

| 3. | Installi   | ing the Board                            | 17 |

|    | 3.1 Hot 9  | Swap Insertion Procedures                | 17 |

|    | 3.2 Hot 9  | Swap Extraction Procedures               | 18 |

|    |            | nory                                     |    |

|    | 3.3.1      | Memory List and Characteristics          |    |

|    | 3.4 Softv  | ware                                     | 19 |

|    | 3.5 Syste  | em Access                                | 19 |

|    | 3.5.1      | Front Port Serial Connection             | 19 |

| 4. | Therma     | al Considerations                        | 22 |

|    | 4.1 Ther   | mal Monitoring                           | 22 |

|    |            | rnal Thermal Regulation                  |    |

|    | 4.2.1      | Forced Airflow                           |    |

|    | 4.2.2      | Thermal Characteristic Graphs            | 23 |

|    | 4.2.3      | Airflow Impedance                        | 25 |

|    | 4.2.4      | Airflow Paths                            | 25 |

| 5. | Softwa     | re Setup                                 | 28 |

|    | 5.1 MMC    | Firmware                                 | 28 |

|    | 5.1.1      | Related Documentation                    |    |

|    | 5.1.2      | IPMI Sensors                             | 29 |

|    | 5.1.3      | Field Replaceable Unit (FRU) Information | 36 |

|    | 5.1.4      | E-Keying                                 |    |

|    | 5.1.5      | Watchdog                                 | 37 |

|    | 5.1.6      | MMC Firmware Code                        | 37 |

|    | 5.1.7      | Updating MMC Firmware                    | 38 |

|    | 5.1.8      | Override AMC.0 R2 support                | 38 |

|    | 5.2 Boar   | rd Firmware                              | 38 |

|    | 5.2.1      | Switching between Firmware Images        | 40 |

|    | 5.3 Boot  | loader                                             | 40  |

|----|-----------|----------------------------------------------------|-----|

|    | 5.3.1     | Bootloader shell and options                       | 40  |

|    | 5.3.2     | Protected variables                                | 43  |

|    | 5.3.3     | NetConsole                                         | 43  |

|    | 5.3.4     | Booting Embedded Linux firmware from eUSB device   | 44  |

|    | 5.3.5     | U-boot memory configurations                       | 44  |

|    | 5.3.6     | Network interfaces                                 | 45  |

|    | 5.3.7     | Bootloader Update                                  | 45  |

|    | 5.3.8     | Embedded Linux update                              | 46  |

|    | 5.4 Emb   | edded Linux                                        | 47  |

|    | 5.4.1     | Embedded filesystem and init script customizations | 47  |

|    | 5.4.2     | Access to NFS share from Cavium Embedded Linux     | 47  |

|    | 5.4.3     | eUSB Storage                                       | 47  |

|    | 5.4.4     | Booting over PCI (oct-remote-boot)                 | 47  |

|    | 5.4.5     | Onboard flash access within Cavium Embedded Linux  | 48  |

|    | 5.4.6     | Ethernet over Serial Rapid IO                      | 49  |

|    | 5.5 Usin  | g CFGT00L                                          | 49  |

|    | 5.5.1     | Usage                                              | 49  |

|    | 5.6 Caviu | um Linux BSP                                       | 54  |

|    | 5.6.1     | Requirements                                       | 54  |

|    | 5.6.2     | Install Instructions                               | 54  |

|    | 5.6.3     | Build                                              | 55  |

|    | 5.6.4     | Simple executive applications                      | 55  |

| Α. | Connec    | tors Pinouts                                       |     |

|    |           | SSD Flash Module                                   |     |

|    |           | Front IO                                           |     |

|    |           | al Port Pinout                                     |     |

| _  |           |                                                    |     |

| В. | _         | Help                                               |     |

|    |           | rning Defective Merchandise                        |     |

|    | B.2 When  | n Returning a Unit                                 | B-3 |

| С. | Glossar   | y                                                  |     |

# **List of Figures**

| Figure | 2-1: Block Diagram                                                        |     |

|--------|---------------------------------------------------------------------------|-----|

| Figure | 2-2: AM4211 Quick Reference Sheet                                         |     |

| Figure | 2-3: Front Panel of AM4211                                                | .14 |

| Figure | 3-1: Approved Memory List                                                 | .19 |

| Figure | 4-1: Temperature Sensor Locations (AM4211 Top View, heat sinks not shown) | .22 |

| Figure | 4-2: 100% Operational Limits for the AM4211                               | .24 |

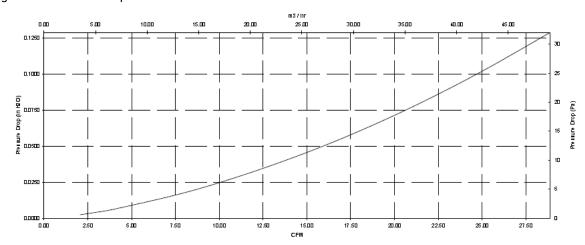

| Figure | 4-3: AM4211 Impedance Curve                                               | .2! |

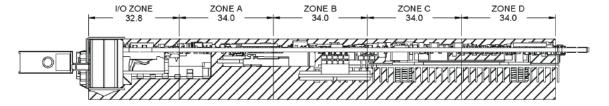

| Figure | 4-4: Thermal Zones of the AM4211                                          | .25 |

## **List of Tables**

| Table 1-1  | Board Specifications                             | . 3 |

|------------|--------------------------------------------------|-----|

| Table 1-2  | AM4211 Software Specification                    | 5   |

| Table 2-1  | SFP+ Connection                                  | 10  |

| Table 2-2  | SFP+ LED Significations                          | 10  |

| Table 2-3  | AMC Port Assignment                              | 13  |

| Table 2-4  | Hot Swap LED                                     | 14  |

| Table 2-5  | Red LED                                          | 14  |

| Table 2-6  | Amber/Green LED                                  | 15  |

| Table 2-7  | Amber/Green LED                                  | 15  |

| Table 4-1  | MMC Temperature Sensors Thresholds               | 23  |

| Table 4-2  | Deviation of the Airflow Rate on the AM4211      | 26  |

| Table 5-1  | Sensor list                                      | 29  |

| Table 5-2  | Kontron FRU info agent sensor                    | 33  |

| Table 5-3  | Kontron IPMB-L Link sensor                       | 34  |

| Table 5-4  | Kontron MMC FW upgrade status sensor             | 34  |

| Table 5-5  | Kontron reset sensor                             | 35  |

| Table 5-6  | Kontron user SW upgrade status sensor            | 35  |

| Table 5-7  | Voltage sensor thresholds                        | 36  |

| Table 5-8  | Fabric Default Flash Sector to Image Association | 38  |

| Table 5-9  | Swapped Flash Sector to Image Association        | 38  |

| Table 5-10 | On-board 128 MB NOR Flash layout                 | 39  |

| Table 5-11 | Bootloader environment variables                 | 41  |

| Table 5-12 | Bootloader network interfaces                    | 45  |

| Table 5-13 | Embedded Linux MTD partitions                    | 48  |

| Table 5-14 | SRTO MAC adress                                  | 49  |

vi AM4211

## **Safety Instructions**

### **Before You Begin**

Before handling the board, read the instructions and safety guidelines on the following pages to prevent damage to the product and to ensure your own personal safety. Refer to the "Advisory Convention" section in the Preface for advisory conventions used in this user's guide, including the distinction between Warnings, Cautions, Important Notes, and Notes.

- Always use caution when handling/operating the computer. Only qualified, experienced and authorized electronics service personnel should access the interior of the computer. The power supplies produce high voltages and energy hazards, which can cause bodily harm.

- Use extreme caution when installing or removing components. Refer to the installation instructions in this user's guide for precautions and procedures. If you have any questions, please contact Kontron Technical Support.

#### WARNING

High voltages are present inside the chassis when the unit's power cord is plugged into an electrical outlet. Turn off system power, turn off the power supply, and then disconnect the power cord from its source before removing the chassis cover. Turning off the system power switch does not remove power to components.

vii AM4211

### **Preventing Electrostatic Discharge**

Static electricity can harm system boards. Perform service at an ESD workstation and follow proper ESD procedure to reduce the risk of damage to components. Kontron strongly encourages you to follow proper ESD procedure, which can include wrist straps and smocks, when servicing equipment.

Take the following steps to prevent damage from electrostatic discharge (ESD):

- When unpacking a static-sensitive component from its shipping carton, do not remove the

component's antistatic packing material until you are ready to install the component in a

computer. Just before unwrapping the antistatic packaging, be sure you are at an ESD workstation

or grounded. This will discharge any static electricity that may have built up in your body.

- When transporting a sensitive component, first place it in an antistatic container or packaging.

- Handle all sensitive components at an ESD workstation. If possible, use antistatic floor pads and workbench pads.

- Handle components and boards with care. Don't touch the components or contacts on a board. Hold a board by its edges.

- Do not handle or store system boards near strong electrostatic, electromagnetic, magnetic or radioactive fields.

viii AM4211

## **Safety Requirements**

The following safety precautions must be observed when installing or operating the AM4211. Kontron assumes no responsibility for any damage resulting from failure to comply with these requirements.

#### WARNING

Due care should be exercised when handling the board due to the fact that the heat sink can get very hot. Do not touch the heat sink when installing or removing the board.

In addition, the board should not be placed on any surface or in any form of storage container until the board and heat sink have cooled down. Remove the such time as have cooled down to room temperature.

#### **ESD Equipment**

This AMC board contains electrostatically sensitive devices. Please observe the necessary precautions to avoid damage to your board:

- Discharge your clothing before touching the assembly. Tools must be discharged before use.

- Do not touch components, connector-pins or traces.

- If working at an anti-static workbench with professional discharging equipment, please do not omit to use it.

#### WARNING

This product has gold conductive fingers which are susceptible to contamination. Take care not to touch the gold conductive fingers of the AMC Card-edge connector when handling the board.

Failure to comply with the instruction above may cause damage to the board or result in improper system operation.

#### **CAUTION**

Laser light from fiber-optic transmission cables and components can damage your eyes. The laser components plugged into the switch are Class 1 laser components. Class 1 laser is considered incapable of producing damaging radiation levels during normal operation or maintenance.

To avoid damaging your eyes and to continue safe operation in case of abnormal circumstances:

- Never look directly into the outlets of fiber-optic transmission components or fiber-optic cables with unprotected eyes.

- Never allow fiber-optic transmission path to operate until all the connections have been made.

Always fit protective plugs to any unused ports of the switch.

#### WARNING

Be careful when inserting or removing the AM4211. The SFP+ cage has sharp edges which might lead to injuries.

ix AM4211

## **Preface**

### **How to Use This Guide**

This user's guide is designed to be used as step-by-step instructions for installation, and as a reference for operation, troubleshooting and upgrades.

For the circuits, descriptions and tables indicated, Kontron assumes no responsibility as far as patents or other rights of third parties are concerned.

The following is a summary of chapter contents:

- Chapter 1, Product Description

- Chapter 2, Board Features

- Chapter 3, Installing the board

- Chapter 4, Thermal

- Chapter 5, Software Setup

- Appendix A, Connector Pinouts

- Appendix B, Getting Help

- Appendix C, Glossary

### **Customer Comments**

If you have any difficulties using this user's guide, discover an error, or just want to provide some feedback, please send a message to: <a href="mailto:Tech.Writer@ca.kontron.com">Tech.Writer@ca.kontron.com</a>. Detail any errors you find. We will correct the errors or problems as soon as possible and post the revised user's guide on our Web site. Thank you.

### **Advisory Conventions**

Seven types of advisories are used throughout the user guides to provide helpful information or to alert you to the potential for hardware damage or personal injury. They are Note, Signal Paths, Jumpers Settings, BIOS Settings, Software Usage, Cautions, and Warnings. The following is an example of each type of advisory. Use caution when servicing electrical components.

#### Note:

Indicates information that is important for you to know.

#### **Signal Path:**

Indicates the places where you can find the signal on the board.

#### **Jumper Settings:**

Indicate the jumpers that are related to this section.

### **BIOS Settings:**

Indicates where you can set this option in the BIOS.

### Software Usage:

Indicates how you can access this feature through software.

#### **CAUTION**

Indicates potential damage to hardware and tells you how to avoid the problem.

#### WARNING

Indicates potential for bodily harm and tells you how to avoid the problem.

#### **ESD Sensitive Device:**

This symbol and title inform that electronic boards and their components are sensitive to static electricity. Therefore, care must be taken during all handling operations and inspections of this product, in order to ensure product integrity at all times.

Please read also the section "Special Handling and Unpacking Instructions".

#### **CE Conformity:**

This symbol indicates that the product described in this manual is in compliance with all applied CE standards. Please refer also to the section "Regulatory Compliance Statements" in this manual.

Disclaimer: We have tried to identify all situations that may pose a warning or a caution condition in this user's guide. However, Kontron does not claim to have covered all situations that might require the use of a Caution or a Warning.

i AM4211

## **Unpacking**

Follow these recommendations while unpacking:

- Remove all items from the box. If any items listed on the purchase order are missing, notify Kontron customer service immediately.

- Inspect the product for damage. If there is damage, notify Kontron customer service immediately.

- Save the box and packing material for possible future shipment.

xii AM4211

## **Regulatory Compliance Statements**

### FCC Compliance Statement for Class B Devices

This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to Part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference in a residential installation. This equipment generated, uses and can radiate radio frequency energy and, if not installed and used in accordance with the instructions may cause harmful interference to radio communications. However, there is no guarantee that interference will not occur in a particular installation. If this equipment does cause harmful interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one or more of the following measures:

- Reorient or relocate the receiving antenna.

- Increase the separation between the equipment and receiver.

- Connect the equipment into an outlet on a circuit different from that to which the receiver is connected.

- Consult the dealer or an experience radio/TV technician for help.

#### WARNING

This is a Class B product. If not installed in a properly shielded enclosure and used in accordance with this User's Guide, this product may cause radio interference in which case users may need to take additional measures at their own expense.

### Safety Certification

All Kontron equipment meets or exceeds safety requirements based on the IEC/EN/UL/CSA 60950-1 family of standards entitled, "Safety of information technology equipment." All components are chosen to reduce fire hazards and provide insulation and protection where necessary. Testing and reports when required, are performed under the international IECEE CB Scheme. Please consult the "Kontron Safety Conformity Policy Guide" for more information.

### **CE Certification**

The product(s) described in this user's guide complies with all applicable European Union (CE) directives if it has a CE marking. For computer systems to remain CE compliant, only CE-compliant parts may be used. Maintaining CE compliance also requires proper cables and cabling techniques. Although Kontron offers accessories, the customer must ensure that these products are installed with proper shielding to maintain CE compliance. Kontron does not offer engineering services for designing cabling systems. In addition, Kontron will not retest or recertify systems or components that have been reconfigured by customers.

xiii AM4211

## **Limited Warranty**

Kontron grants the original purchaser of Kontron's products a TWO YEAR LIMITED HARDWARE WARRANTY as described in the following. However, no other warranties that may be granted or implied by anyone on behalf of Kontron are valid unless the consumer has the express written consent of Kontron.

Kontron warrants their own products, excluding software, to be free from manufacturing and material defects for a period of 24 consecutive months from the date of purchase. This warranty is not transferable nor extendible to cover any other users or long- term storage of the product. It does not cover products which have been modified, altered or repaired by any other party than Kontron or their authorized agents. Furthermore, any product which has been, or is suspected of being damaged as a result of negligence, improper use, incorrect handling, servicing or maintenance, or which has been damaged as a result of excessive current/voltage or temperature, or which has had its serial number(s), any other markings or parts thereof altered, defaced or removed will also be excluded from this warranty.

If the customer's eligibility for warranty has not been voided, in the event of any claim, he may return the product at the earliest possible convenience to the original place of purchase, together with a copy of the original document of purchase, a full description of the application the product is used on and a description of the defect. Pack the product in such a way as to ensure safe transportation.

Kontron provides for repair or replacement of any part, assembly or sub-assembly at their own discretion, or to refund the original cost of purchase, if appropriate. In the event of repair, refunding or replacement of any part, the ownership of the removed or replaced parts reverts to Kontron, and the remaining part of the original guarantee, or any new guarantee to cover the repaired or replaced items, will be transferred to cover the new or repaired items. Any extensions to the original guarantee are considered gestures of goodwill, and will be defined in the "Repair Report" issued by Kontron with the repaired or replaced item.

Kontron will not accept liability for any further claims resulting directly or indirectly from any warranty claim, other than the above specified repair, replacement or refunding. In particular, all claims for damage to any system or process in which the product was employed, or any loss incurred as a result of the product not functioning at any given time, are excluded. The extent of Kontron liability to the customer shall not exceed the original purchase price of the item for which the claim exists.

Kontron issues no warranty or representation, either explicit or implicit, with respect to its products reliability, fitness, quality, marketability or ability to fulfil any particular application or purpose. As a result, the products are sold "as is," and the responsibility to ensure their suitability for any given task remains that of the purchaser. In no event will Kontron be liable for direct, indirect or consequential damages resulting from the use of our hardware or software products, or documentation, even if Kontron were advised of the possibility of such claims prior to the purchase of the product or during any period since the date of its purchase.

Please remember that no Kontron employee, dealer or agent is authorized to make any modification or addition to the above specified terms, either verbally or in any other form, written or electronically transmitted, without the company's consent.

xiv AM4211

## Chapter 1

# **Product Description**

| 1.1 | Product Overview     | 2 |

|-----|----------------------|---|

|     | What's Included      |   |

|     | Board Specifications |   |

|     | Hot Swap Capability  |   |

|     | Software Support     |   |

## 1. Product Description

### 1.1 Product Overview

The AM4211 is an Advanced Mezzanine Card (AMC) from Kontron supporting the Cavium OCTEON II CN6645 Network Service Processor. It is cost and performance competitive with other NSP AdvancedMC cards featuring similar number of cores and process technology. The big advantage of the Cavium NSP is it's broad market acceptance and large ecosystem solution providers. It is also an excellent choice for future upgrade to the existing Cavium OCTEON Plus AM42xx series offered by Kontron.

The AM4211 is a 10 GbE card with one 10 Gb Ethernet port on front panel using a SFP+ cage and software configurable Interfaces to the Fabric side (one PCIe/SRIO on ports 4 to 7 and one PCIe/SGMII/XAUI on ports 8 to 11).

Two Gigabit Ethernet Ports are connected to ports 0 and 1 of the AMC connector.

A debug port is accessible via a low profile serial port connector on front plate or AMC port 15 of Extended Option Region. Two different UART can be routed at the same time in two differents places (ex: CPU UARTO to front, CPU UART1 to rear).

An eUSB mezzanine that has a capacity of up 16 GB is available for storage.

### 1.2 What's Included

This board is shipped with the following items:

- One AM4211 AMC board;

- One Quick Reference Sheet;

- One low profile serial port to D-sub (female) adapter cable (1016-6698);

- One Documentation & Drivers disk;

If any item is missing or damaged, contact your supplier.

## **1.3** Board Specifications

Table 1-1: Board Specifications

| Features                            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Multicore Processor Unit            | <ul> <li>CN6645 Cavium OCTEON II processor capable of supporting 10 Cores at 1.1 GHz</li> <li>Socketless</li> </ul>                                                                                                                                                                                                                                                                                                                                                                         |

| Memory                              | <ul><li>1 to 32 GB DDR3 Memory support with ECC</li><li>Up to 1333 MHz ECC SO-DIMM</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                |

| Flash Memory                        | <ul><li>128MB NOR Flash</li><li>Boot sector protection</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                            |

| eUSB Storage                        | Single Port USB 2.0 interface                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Dual Gigabit Ethernet<br>Controller | <ul> <li>Dual Gigabit Ethernet Controller Broadcom BCM5482</li> <li>SGMII interface to processor</li> <li>2 1000Base-BX (Serdes) interfaces to AMC connector</li> </ul>                                                                                                                                                                                                                                                                                                                     |

| IPMI                                | <ul> <li>IPMI 2.0 compliant</li> <li>Voltage and Temperature Sensors</li> <li>ATCA LED control</li> <li>FRU data storage for AMC</li> <li>Firmware Update handling for field upgrades, rollbacks and watchdog functions</li> </ul>                                                                                                                                                                                                                                                          |

| I/0 Interfaces                      | <ul> <li>Front: 1 SFP+ cage to support multi-rate fiber SFP+ modules</li> <li>Front: low profile connector for RS232 access to Processor</li> <li>AMC TCLKA and TCLKC support</li> <li>AMC FCLKA input with 100MHz</li> <li>AMC Port 0 and Port 1: 1000Base-BX</li> <li>AMC port 4 to 7: Configurable PCIe Gen 2 5 GT/s x4 or SRIO x4 Level I (up to 3.125 GBaud)</li> <li>AMC port 8 to 11: PCIe Gen2 5GT/s x4, XAUI or SGMII</li> <li>AMC Port 15: RS232 (proprietary mapping)</li> </ul> |

| Features                         | Description                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Standards Compliance             | <ul> <li>This board is compliant to the following standards:</li> <li>AMC.0 R2.0 Advance Mezzanine Card Base Specification</li> <li>AMC.1 R2.0 PCI Express and Advance Switching</li> <li>AMC.2 R1.0 Ethernet Specification</li> <li>AMC.4 R1.0 Serial RapidIO Specification</li> <li>MTCA.0 R1.0 Micro Telecommunication Computing Architecture Base Specification</li> <li>IPMI v2.0.</li> <li>RoHS compliant.</li> </ul> |

| Mechanical<br>Characteristics    | 4HP single Mid-size AMC Module                                                                                                                                                                                                                                                                                                                                                                                              |

| Operating Voltages               | <ul> <li>Management: 3.3V +/-0.3V</li> <li>Payload: 10VDC to 14VDC</li> </ul>                                                                                                                                                                                                                                                                                                                                               |

| Operation Power                  | <ul> <li>Management: 0.495 W max., TBD W typ.</li> <li>Payload: 40 W max., TBD W typ.</li> </ul>                                                                                                                                                                                                                                                                                                                            |

| Temperature                      | <ul> <li>Operates from -5°C to 55°C ambient air temperature with forced convection. Based on B.4. chassis.</li> <li>Operating @ 8 CFM: up to 25°C</li> <li>Operating @ 11.4 CFM: 26°C to 40°C</li> <li>Operating @ 18.0 CFM: 41°C to 55°C</li> <li>Non-Operating: -40°C to 85°C</li> </ul>                                                                                                                                  |

| Humidity                         | <ul> <li>Designed to meet Bellcore GR-63, Section 4.1</li> <li>Operating: 5%-93% (non-condensing) at 40°C</li> <li>Non-Operating: 5%-93% (non-condensing) at 40°C</li> </ul>                                                                                                                                                                                                                                                |

| Altitude                         | <ul> <li>Designed to meet the following requirements according to Belcore GR-63, section 4.1.3:</li> <li>Operating: -300 m to 4,000 m (13123 ft) (GR63 4.1.3), may require additional cooling above 1800m (5905ft)</li> <li>Non-Operating: -300 m to 14,000 m (45931.2 ft)</li> </ul>                                                                                                                                       |

| Shock & Vibration                | <ul> <li>Designed to meet EN 300 019 and Telcore GR-63</li> <li>Designed to meet NEBS Level 3, Earthquake Zone 4</li> </ul>                                                                                                                                                                                                                                                                                                 |

| Safety                           | <ul> <li>Low Voltage Directive 2006/95/EC</li> <li>Complies with IEC/EN/CSA/ UL 60950-1</li> <li>The board meets flammability requirement, as specified in Telcordia GR-63</li> <li>UL 94V-0/1 with Oxygen index of 28% or greater material</li> </ul>                                                                                                                                                                      |

| Electromagnetic<br>Compatibility | <ul> <li>Meets or exceeds the following specifications (assuming an adequate chassis):</li> <li>EMC Directive 2004/108/EC</li> <li>EN55022; EN55024; CISPR22; VCCI</li> <li>EN 300 386</li> <li>FCC 47 CFR Part 15</li> <li>Telcordia GR-1089</li> </ul>                                                                                                                                                                    |

## 1.4 Hot Swap Capability

The AMC supports Full Hot Swap capability as required by AMC.0 R2.0. It can be removed from or installed in the system while it is on (without powering-down the system). Please refer to the AMC.0 R2.0 specification for additional details.

## **1.5** Software Support

The following table contains information related to software supported by the AM4211.

Table 1-2: AM4211 Software Specification

|                  | Specifications                                                                                                                                                                                                                                                                                                                                                                       |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General          | <ul> <li>The system supports IPMI version 2.0 for board level management (AMC.0).</li> <li>Support for onboard IPMI event log (SEL)</li> <li>Reliable field upgrades for all software components, including boot loader and IPMI firmware</li> <li>Optional Dual boot images with roll-back capability.</li> <li>Offline Diagnostic software for running diagnostic tests</li> </ul> |

| Bootloader       | U-Boot  Power On Self Test  Loadable boot image from onboard flash  Reliable field upgradable  KCS interface to MMC  Serial console support                                                                                                                                                                                                                                          |

| Operating System | Linux Operating System is based on Cavium SDK 2.2.0 (2.6.32).                                                                                                                                                                                                                                                                                                                        |

## Chapter 2

# **Board Features**

| 2.1 | Block Diagram              | 7  |

|-----|----------------------------|----|

|     | System Core                |    |

|     | eUSB Storage               |    |

|     | SFP+ Front IO              |    |

|     | Gigabit Ethernet           |    |

|     | Serial Rapid I/O (SRIO)    |    |

|     | PCIe                       |    |

| 2.8 | SGMII / XAUI               | 12 |

|     | RS232 Management Interface |    |

|     | IPMI                       |    |

|     | AMC Connector              |    |

|     | Front Panel LEDs           |    |

## 2. Board Features

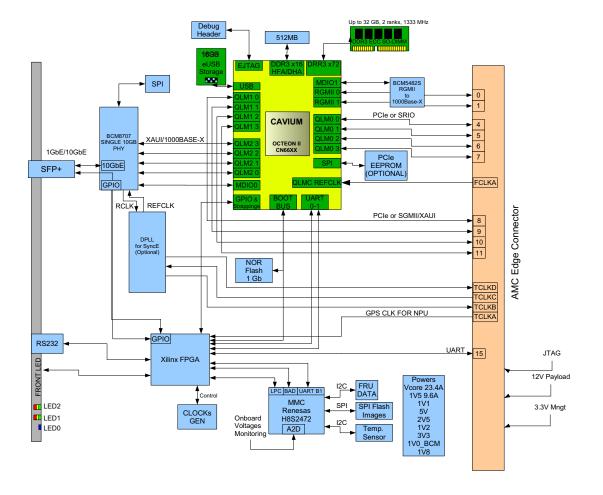

## 2.1 Block Diagram

Figure 2-1:Block Diagram

## 2.2 System Core

### 2.2.1 Cavium OCTEON II CN6645

- Ten(10) Cores at 1.1GHz

- Up to 30 Billion MIPS64 instructions per second

- 12 high-speed SERDES, flexibly configured in blocks of 4 (referred to as QLM)

- XAUI, SGMII, PCIe or SRIO depending on QLM

- Integrated coprocessors for application acceleration, including: Packet I/O processing, QoS, TCP Acceleration; Support for IPsec, SSL, SRTP, WLAN and 3G/UMB/LTE security (includes DES, 3DES, AES-GCM, AES up to 256, SHA1, SHA-2 up to SHA-512, RSA up to 8192, DH, KASUMI); and Compression/Decompression with up to 10Gbps throughput and highest compression ratios.

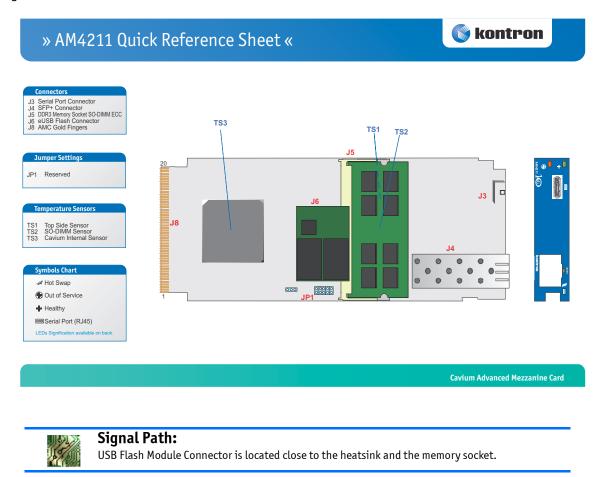

## 2.3 eUSB Storage

The AM4211 supports one (1) Solid State Drive. It is a NAND flash disk module with a USB 2.0 interface. The module is connected to a 2x5 header (refers to J6 on showed in Figure 2-2) on the AM4211 board.

Figure 2-2:AM4211 Quick Reference Sheet

### 2.4 SFP+ Front IO

The front SFP+ cage supports a multi-rate fiber SFP+ module.

Table 2-1: SFP+ Connection

| SFP+ | Connection  |

|------|-------------|

| 1    | 10 GbE XAUI |

SFP+ module is not provided with the AM4211 and has to be obtained separately. The SFP+ uplink port is compliant to the Enhanced 8.5 and 10 Gigabit Small Form Factor Pluggable Module "SFP+" MultiSource Agreement (MSA), February 16th 2007, and the Improved Pluggable Formfactor MSA, February 26th 2007. An application note with a list of SFP+ modules successfully operated by Kontron in the AM4211 is available upon request.

#### **CAUTION LASER LIGHT!**

Do not look into the laser beam!

The SFP+ module is fitted with a class 1 or 1M laser. To avoid possible exposure to hazardous levels of invisible laser radiation, do not exceed maximum ratings.

The SFP+ port has a bi-color green/amber LED with the following signification:

Table 2-2: SFP+ LED Significations

| LED         | Signification   |

|-------------|-----------------|

| Green on    | Link 10Gbit     |

| Green blink | Activity 10Gbit |

| Amber on    | Link 1000Mbit   |

### 2.5 Gigabit Ethernet

Two Gigabit Ethernet Ports are connected to ports 0 and 1 of the AMC connector.

#### **Signal Path:**

Two Gigabit Ethernet Ports are connected to ports 0 and 1 of the AMC connector.

## 2.6 Serial Rapid I/O (SRIO)

AMC provides SRIO x4 interfaces only as per AMC.4 R1.0 fat pipe region on ports 4 to 7. The supported SRIO speed are using a priority order controlled by E-Keying mechanism.

SRIO speed priority list:

SRIO 3.125Gbs

SRIO 2.5Gbs

SRIO 1.25Gbs

#### **Signal Path:**

Serial Rapid I/O is connected to ports 4 to 7 of the AMC connector.

### **2.7 PCIe**

AMC provides two independant PCIe links. A PCIe x4 Gen2 interface on fat pipe region ports 4 to 7 as per AMC.1 R2.0. And a PCIe x4 Gen2 interface on the extended fat pipe region ports 8 to 11. The supported PCIe modes are using a priority order controlled by E-Keying mechanism.

PCIe mode priority list:

PCIe Gen2 x4 SCC

PCIe Gen2 x4 NoSCC

PCIe Gen2 x1 SCC

PCIe Gen2 x1 NoSCC

PCIe Gen1 x4 SCC

PCIe Gen1 x4 NoSCC

PCIe Gen1 x1 SCC

PCIe Gen1 x1 NoSCC.

### Signal Path:

PCIe is connected to ports 4 to 7 and 8 to 11 of the AMC connector.

## 2.8 SGMII / XAUI

One SGMII / XAUI interface, as per AMC.2 R1.0, is available on ports 8 to 11 in the fat pipes region.

#### Signal Path:

The SGMII / XAUI is connected to ports 8 to 11 of the AMC connector.

### 2.9 RS232 Management Interface

The RS232 interface of the OCTEON is connected to the front panel low profile connector.

Use a special cable with low profile serial port connector to SubD connector.

#### **Signal Path:**

The serial port is available through the AMC faceplate.

### 2.10 IPMI

The AM4211 supports an intelligent hardware management system based on the Intelligent Platform Management Interface (IPMI) Specification 2.0. It provides the ability to manage the power, cooling and interconnect needs of intelligent devices, to monitor events and to log events to a central repository.

The MMC ("Module Management Controller") controls all hotswap and E-Keying processes required by ATCA. It activates the board power supply and enables communication with the AMC carrier. The MMC manages the Ethernet switch E-Keying and the baseboard ATCA feature. The controller is connected to the IPMC of the ATCA carrier board via IPMB-L bus.

All voltages and currents on the board are monitored by the MMC. Three temperature sensors on the board make sure that thermal conditions are met:

- Temp NPU (OCTEON Internal Sensor)

- Temp MMC

- Temp DIMM

For more information on the thermal design and management, consult the "Thermal Consideration" section.

## 2.11 AMC Connector

Table 2-3: AMC Port Assignment

| Port  | Region   | Connection                                                                       |

|-------|----------|----------------------------------------------------------------------------------|

| 0     | GbE      | GbE eth0                                                                         |

| 1     | GbE      | GbE eth1                                                                         |

| 2     | Storage  | -                                                                                |

| 3     | Storage  | -                                                                                |

| 4     | Fat Pipe | PCIe / SRIO Port 0 (Lane 0)                                                      |

| 5     | Fat Pipe | PCIe / SRIO Port 0 (Lane 1)                                                      |

| 6     | Fat Pipe | PCIe / SRIO Port 0 (Lane 2)                                                      |

| 7     | Fat Pipe | PCIe / SRIO Port 0 (Lane 3)                                                      |

| 8     | Fat Pipe | PCIe / XAUI / SGMII Port 1 (Lane 0)                                              |

| 9     | Fat Pipe | PCIe / XAUI / SGMII Port 1 (Lane 1)                                              |

| 10    | Fat Pipe | PCIe / XAUI / SGMII Port 1 (Lane 2)                                              |

| 11    | Fat Pipe | PCIe / XAUI / SGMII Port 1 (Lane 3)                                              |

| 12    | Extended | +                                                                                |

| 13    | Extended | H.                                                                               |

| 14    | Extended | +                                                                                |

| 15    | Extended | RS232                                                                            |

| 17    | Extended | +                                                                                |

| 18    | Extended | H.                                                                               |

| 19    | Extended | -                                                                                |

| 20    | Extended | H.                                                                               |

| TCLKA | Clock    | For GPS clock from AMC Connector                                                 |

| TCLKB | Clock    | Optional SyncE to the AMC Connector                                              |

| TCLKC | Clock    | Optional SyncE from AMC Connector                                                |

| TCLKD | Clock    | Optional SyncE to the AMC Connector                                              |

| FCLKA | Clock    | PCIe Reference Clock (FCLKA input may be damaged if driven by an M-LVDS driver.) |

### 2.12 Front Panel LEDs

Figure 2-3: Front Panel of AM4211

### 2.12.1 Hot Swap LED (Blue LED)

The AM4211 board supports a blue Hot Swap LED mounted on the front panel. This LED indicates when it is safe to remove the Module. The on-board MMC drives this LED to indicate the hot swap state but is controlled by the carrier's IPMC or the MicroTCA carrier manager. The following states are possible:

Table 2-4: Hot Swap LED

| LED state   | Description                                                                            |

|-------------|----------------------------------------------------------------------------------------|

| OFF         | Module is in M3 or M4 state, normal state when module is in operation.                 |

| ON          | Module is ready for hot swap                                                           |

| Short blink | Module is in M5 state (Deactivation Request) or in M6 state (Deactivation in progress) |

| Long blink  | Activation in progress.                                                                |

### 2.12.2 Out-Of-Service (00S) LED (LED1)

Table 2-5: Red LED

| LED state              | Description                                      |

|------------------------|--------------------------------------------------|

| ON                     | MMC in reset                                     |

| Blinking               | MMC upgrade / rollback in progress               |

| OFF                    | MMC operational                                  |

| Application<br>Defined | May be controlled by application using PICMG API |

## 2.12.3 Health LED (LED2)

Table 2-6: Amber/Green LED

| LED state              | Description                                                              |

|------------------------|--------------------------------------------------------------------------|

| OFF                    | Payload power down                                                       |

| Green                  | Payload is On and no critical event is detected by the sensors           |

| Amber                  | Payload is On and at least one critical event is detected by the sensors |

| Application<br>Defined | May be controlled by application using PICMG API                         |

### 2.12.4 SFP + LED

Table 2-7: Amber/Green LED

| LED state   | Description        |

|-------------|--------------------|

| Green OFF   | no 10GbE link      |

| Green ON    | 10GbE link         |

| Green Blink | 10GbE traffic      |

| Amber OFF   | no 1000Base-x link |

| Amber ON    | 1000Base-x link    |

## Chapter 3

# **Installing the Board**

| 3.1 | Hot Swap Insertion Procedures  | 17 |

|-----|--------------------------------|----|

| 3.2 | Hot Swap Extraction Procedures | 18 |

| 3.3 | Memory                         | 19 |

| 3.4 | Software                       | 19 |

| 3.5 | System Access                  | 19 |

## 3. Installing the Board

### 3.1 Hot Swap Insertion Procedures

The AM4211 is designed for hot swap operation. Hot swapping allows the coordinated insertion and extraction of modules without disrupting other operational elements within the system. This allows for identified faulty elements to be removed and replaced without taking the carrier card out of service that will typically be hosting others modules.

The following procedures are applicable when inserting the AM4211 in a running system.

1 Ensure that the safety requirements are observed.

#### WARNING

Failure to comply with the instruction below may cause damage to the board or result in improper system operation.

2 Ensure that the board is properly configured for operation in accordance with application requirements before installing.

#### WARNING

Care must be taken when applying the procedures below to ensure that neither the AM4211 nor other system boards are physically damaged by the application of these procedures.

- 3 To install the AM4211, perform the following:

- 1 Carefully insert the board into the slot designated by the application requirements until it makes contact with the AMC Card-edge connector located on the carrier or backplane.

- 2 Connect all external interfacing cables to the board as required.

- 3 Using the handle on the front panel, engage the board with the carrier or backplane. When the handle is locked, the board is engaged and the following steps occur:

- 1 The BLUE HS LED turns on.

If the carrier recognizes that the AM4211 is fully seated, the carrier then enables the management power for the AM4211 and the BLUE HS LED turns on.

2 Long blinks of the BLUE HS LED.

If the carrier IPMI controller detects the AM4211, it sends a command to the AM4211 to perform long blinks of the BLUE HS LED.

3 The BLUE HS LED turns off.

The Intelligent Platform Management Controller on the carrier reads the Module Current Requirements record and the AMC Point-to-Point Connectivity record. If the Module FRU information is valid and the carrier can provide the necessary payload power, the BLUE HS

LED will be turned off. If the module FRU information is invalid or the carrier cannot provide the necessary payload power, the insertion process is stopped and the BLUE HS LED keeps blinking. Should this problem occur, please contact Kontron's Technical Support.

4 Short blinks of the Module Management LEDs and the User-Specific LEDs.

The carrier enables the payload power for the AM4211, and the Module Management LEDs and the User-Specific LEDs emit a short blink.

- 5 Ensure that the board and all required interfacing cables are properly secured.

- 4 The AM4211 is now ready for operation. Refer to appropriate AM4211- specific software, application, and system documentation for operating instructions, etc.

## 3.2 Hot Swap Extraction Procedures

To extract the board, proceed as follows:

- 1 Ensure that the safety requirements, listed at page ix above, are observed. Particular attention must be paid to the warning regarding the heat sink!

- 2 Pull the handle on the AM4211's front panel initiating the deactivation. This changes the state of the handle to open. Now, the following steps occur:

- 1 Short blinks of the BLUE HS LED

- When the carrier IPMI controller receives the handle opened event, the carrier sends a command to the MMC with a request to perform short blinks of the BLUE HS LED. This indicates to the operator that the AM4211 is waiting to be deactivated.

- Now the AM4211 waits for a permission from higher level management (Shelf Manager or System Manager) to proceed with its deactivation.

- Once the AM4211 receives the permission to continue the deactivation, all used ports are disabled.

- The Intelligent Platform Management Controller on the Carrier disables the AM4211's Payload Power.

- 2 The BLUE HS LED turns on.

- Now the AM4211 is ready to be safely extracted.

- 3 Disconnect any interfacing cables that may be connected to the AM4211.

- 4 Pull the AM4211 out of the slot. Now the carrier disables the management power for the AM4211.

#### WARNING

Due care should be exercised when handling the board due to the fact that the heat sink can get very hot. Do not touch the heat sink when handling the board.

## 3.3 Memory

The AM4211 has one memory channel connected to the Octeon processor. There is one SO-DIMM populated in an SO-DIMM socket. The AM4211 accepts DDR3, SO-DIMM, registered or unregistered, ECC, x8 or x16, with up to 2 ranks. The DDR3 channel supports data rates up to 1333Mhz. The maximum memory that the board will accept is 32GB, although 8GB is the highest capacity tested to date.

Only use validated memory with this product. Thermal issues or other problems may arise if non-recommended modules are used. At the time of publication of this user guide, the following memories have been qualified and approved. As the memory market is volatile, this list is subject to change, please consult your local technical support for an up to date list.

### 3.3.1 Memory List and Characteristics

Figure 3-1: Approved Memory List

| Manufacturer Part Number | Description                                 | Company        |

|--------------------------|---------------------------------------------|----------------|

| VL41B5263A-K9S           | 4GB 1333MHz unbuffered (SO-UDIMM)           | Virtium        |

| VL43B5263A-K9S           | 4GB 1333MHz registred (SO-RDIMM)            | Virtium        |

| VL41B5663A-F8S           | 2GB 1066MHz unbuffered (SO-UDIMM)           | Virtium        |

| VL41B2863F-F8S           | 1GB unbuffered (SO-UDIMM)                   | Virtium        |

| VR7PU127258GBDK          | 4GB Modular 1 1333MHz unbuffered (SO-UDIMM) | Viking Modular |

| VL41B1G63A-K9S           | 8GB 1333MHz unbuffered (SO-UDIMM)           | Virtium        |

### 3.4 Software

The AM4211 comes as a pre-installed system with all necessary OS, Filesystem, drivers and applications factory-installed with default configurations.

Updating the Software with a new Operating System or applications or new versions is provided by a dedicated update mechanism, which is described under the "Software Setup" section.

### 3.5 System Access

This section gives instructions for accessing the AM4211 using the Serial port via front plate connector.

### 3.5.1 Front Port Serial Connection

The OCTEON II processor's serial console can be accessed directly via the front port connector with the appropriate cabling. The corresponding procedure is described below.

1 Connect the serial port on AM4211 front plate using the RS232 adapter, consult "RS232 Management Interface" section for more details .

Port settings are:

- 115 200 bps

- 8 bit, no parity, 1 stop bit (8N1)

- no flow control

- 2 Ensure that the board is powered up.

- 3 Wait for boot process to complete. Login is not required by default:

```

BusyBox v1.2.1 (2008.09.15-08:10+0000) Built-in shell (ash) Enter 'help' for a list of built-in commands. \sim~^{\pm}

```

## Chapter 4

## **Thermal Considerations**

| 4.1 | Thermal Monitoring          | 22 |

|-----|-----------------------------|----|

| 4.2 | External Thermal Regulation | 23 |

# 4. Thermal Considerations

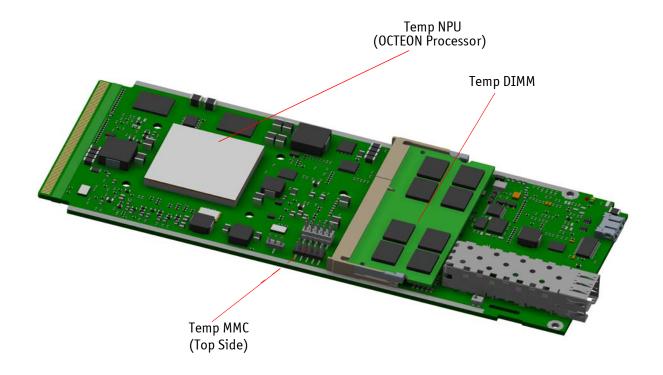

# 4.1 Thermal Monitoring

To ensure optimal operation and long-term reliability of the AM4211, all onboard components must remain within the maximum temperature specifications. Operating the AM4211 above the maximum operating limits will result in permanent damage to the board. To ensure functionality at the maximum temperature, the Module Management Controller supports several temperature monitoring and control features.

The AM4211 includes three temperature sensors that are accessible via the Module Management Controller. Although temperature sensing information is made available to the MMC, the AM4211 itself does not provide any active means of temperature regulation.

Figure 4-1:Temperature Sensor Locations (AM4211 Top View, heat sinks not shown)

The Temp NPU is an on-chip sensor and the Temp MMC sensor is a diode located next to the MMC. The Temp DIMM sensor is a separate sensor measuring the temperature in the memory module. The Dual 10 GE Phy does not have a sensor. Simulations show that its temperature remains uncritical under operating conditions compared to the processor.

The following table shows the temperature thresholds of all three sensors.

Table 4-1:MMC Temperature Sensors Thresholds

| Sensor    | Lower Non<br>Recoverable | Lower Critical | Lower Non<br>Critical | Upper Non<br>Critical | Upper Critical | Upper Non<br>Recoverable |

|-----------|--------------------------|----------------|-----------------------|-----------------------|----------------|--------------------------|

| Temp DIMM | -8°C                     | 0°C            | 5°C                   | 70°C                  | 75°C           | 98°C                     |

| Temp NPU  | -6°C                     | 0°C            | 5°C                   | 85°C                  | 90°C           | 101°C                    |

| Temp MMC  | -8°C                     | 0°C            | 5°C                   | 60°C                  | 65°C           | 72°C                     |

Temperature values are measured with an accuracy of 1°C for the NPU and 3°C for the DIMM and the MMC.

# 4.2 External Thermal Regulation

The external thermal regulation of the AM4211 is realized using a dedicated heat sink design in conjunction with a system chassis that provides thermal supervision, controlled system airflow and thermal protection, such as increased airflow, reduced ambient air temperature, or power removal.

The main heat sink provided on the AM4211 has been specifically designed to ensure the best possible basis for operational stability and long-term reliability. The physical size, shape, and construction of the heat sink ensure the lowest possible thermal resistance. In addition, it has been specifically designed to efficiently support forced airflow concepts as found in modern AMC carriers and MicroTCA systems.

### 4.2.1 Forced Airflow

When developing applications using the AM4211, the system integrator must be aware of the overall system thermal requirements. All system chassis requirements must be provided to make sure they satisfy these requirements. As an aid to the system integrator, characteristic graphs are provided for the AM4211.

#### WARNING

As Kontron assumes no responsibility for any damage to the AM4211 or other equipment resulting from overheating any of the components, it is highly recommended that system integrators as well as end users confirm that the operational environment of the AM4211 complies with the thermal considerations set forth in this document.

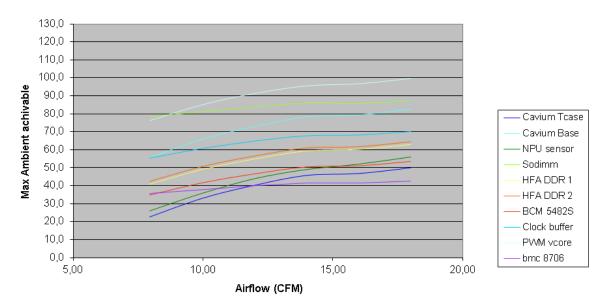

## 4.2.2 Thermal Characteristic Graphs

The thermal characteristic graph shown in the following pages illustrates the maximum ambient air temperature as a function of the linear airflow rate for the power consumption indicated. The diagram is intended to serve as guidance for reconciling board and system, considering the thermal aspect. When operating below the indicated curves, the AMC runs steadily without any intervention of thermal supervision. When operated above the indicated curves, various thermal protection mechanisms may take effect eventually resulting in an emergency stop in order to protect the AMC from thermal destruction. In real applications this means that the board can be operated temporarily at a higher ambient temperature or at a reduced flow rate and still provide some margin for temporarily requested peak performance before thermal protection will be activated.

### 4.2.2.1 How to Read the Diagram

The diagram contains multiple curves displaying the thermal sensors temperature versus the provided airflow and the proper system class required. Full thermal load is not expected to be reached under real operating conditions. For a given flow rate there is a maximum airflow input temperature (= ambient temperature) provided. Below this operating point, a safe operation is guaranteed. Above this operating point, the chassis thermal management must become active and take the necessary steps to protect the AMC from thermal destruction.

#### 4.2.2.2 *Airflow*

At a given cross-sectional area and a required flow rate, an average, homogeneous airflow speed can be calculated using the following formula:

Airflow = Volumetric flow rate / area.

The airflow is specified in m/s = meter-per-second or in LFM = linear-feet-per-minute, respectively.

Conversion: 1 LFM = 0.00508 m/s; 1 m/s = 196.85 LFM

The following figure illustrates the operational limits of the AM4211 taking into consideration power consumption vs. ambient air temperature vs. airflow rate. The values are based on simulation data taking into account the actual power values of all components.

#### WARNING

In all situations, the maximum specified case temperature of the components must be kept below the maximum allowable temperature.

Figure 4-2:100% Operational Limits for the AM4211

#### Max Ambient vs Airflow

# 4.2.3 Airflow Impedance

In order to determine the cooling requirements of the AM4211, the airflow impedance of the module has been determined via simulation. No card guides or struts have been used for the simulations because the resulting airflow impedance depends on individual configuration of the AMC carrier or MicroTCA system.

Figure 4-3: AM4211 Impedance Curve

## 4.2.4 Airflow Paths

The area between the front panel and the AMC Card-edge connector is divided into five zones, one I/O zone and four uniform thermal zones, A, B, C, and D. The PICMG AMC.0 Specification states that the uniformity of the airflow paths' resistance should provide an impedance on the A, B, C, and D zones that is within  $\pm$  25% of the average value of the four thermal zones.

Figure 4-4:Thermal Zones of the AM4211

Table 4-2:Deviation of the Airflow Rate on the AM4211

|      | Inlet Velocity |       |        | Deviat | ion (%) |        |

|------|----------------|-------|--------|--------|---------|--------|

| CFM  | m/s            | LFM   | ZONE A | ZONE B | ZONE C  | ZONE D |

| 2.3  | 0.28           | 55.6  | -26.5  | -12.7  | 22.8    | 16.4   |

| 3.4  | 0.42           | 82.8  | -21.2  | -14.1  | 20.9    | 14.4   |

| 4.5  | 0.56           | 110.0 | -17.7  | -15.2  | 19.3    | 13.6   |

| 9.0  | 1.11           | 219.1 | -10.5  | -16.8  | 15.3    | 12.0   |

| 13.6 | 1.68           | 329.7 | -6.9   | -17.0  | 12.8    | 11.0   |

| 18.3 | 2.25           | 442.4 | -4.6   | -16.6  | 11.0    | 10.1   |

| 22.9 | 2.82           | 555.1 | -2.5   | -15.6  | 9.2     | 8.9    |

| 27.6 | 3.40           | 668.8 | -1.0   | -15.1  | 7.9     | 8.2    |

| 32.3 | 3.98           | 782.5 | 0.1    | -14.2  | 63.9    | 7.2    |

# Chapter 5

# **Software Setup**

| 5.1 | MMC Firmware     | 28 |

|-----|------------------|----|

|     | Board Firmware   |    |

|     | Bootloader       |    |

| 5.4 | Embedded Linux   | 47 |

| 5.5 | Using CFGTOOL    | 49 |

|     | Cavium Linux RSP |    |

# 5. Software Setup

## 5.1 MMC Firmware

The Module Management Controller (MMC) is a crucial component of any AMC module. Besides acting as a regular IPMI management controller (sensor monitoring, event generation, etc.), it also provides an interface to all necessary data related to module power requirements and implemented interfaces (E-Keying). Further, it plays an active role in the module hot swap state management. The carrier IPMI Controller (IPMC) communicates with the MMC using the local IPMB (IPMB-L) bus. In an ATCA/AMC environment, it is the IPMC that actually turns on/off module (payload) power. However, before the IPMC enables the module payload power, various criteria must be satisfied by both the carrier and the module, including handle switch state, power requirements and capabilities, matching interfaces, current module hot swap state, and any other special conditions as specified by the Shelf Manager policy.

### **5.1.1** Related Documentation

IPMI specifications: (http://www.intel.com/design/servers/ipmi/spec.htm)

- IPMI-Intelligent Platform Management Interface Specification. Second Generation v2.0, February 12, 2004 (part)

- IPMI- Platform Management FRU Information Storage Definition v1.0, Document Revision 1.1, September 1999

PICMG specifications: http://www.picmq.org

- PICMG® AMC.0 R2.0 Advanced Mezzanine Card Base Specification

- PICMG® AMC.1 R1.0 PCI Express and Advanced Switching on AdvancedMC

- PICMG® AMC.2 R1.0 AMC Gigabit Ethernet/10 Gigabit XAUI Ethernet

Open tools documentation

- Ipmitool documentation: <a href="http://ipmitool.sourceforge.net">http://ipmitool.sourceforge.net</a>

- OpenIPMI documentation: <a href="http://www.openipmi.sourceforge.net">http://www.openipmi.sourceforge.net</a>

The AM4211 is built in accordance to the AMC.0 R2.0 specification, and is also AMC.1 and AMC.2 compliant and is easily managed via IPMI v1.5/v2.0.

### 5.1.2 IPMI Sensors

The MMC includes many sensors for voltage or temperature monitoring and various others for pass/fail type signal monitoring.

Every sensor is associated with a Sensor Data Record (SDR). Sensor Data Records contain information about the sensors identification such as sensor type, sensor name and sensor unit. SDRs also contain the configuration of a specific sensor such as threshold/hystheresis, event generation capabilities that specifies sensor behavior. Some field of the sensor SDR are configurable through IPMI v1.5 command and are set to built-in initial values. The sensor also includes a field, identifying the sensor owner's address in the system. This allows the carrier to pre-pend an appropriate code when the SDR is scanned so the reader of the sensor list can determine which sensors belong to which physical board in the ATCA carrier or uTCA system.

From an IPMI perspective, the MMC is set up as a satellite management controller (SMC). It does support sensor devices, and uses the IPMI static sensor population feature of IPMI v1.5. All SDRs can be queried using Device SDR commands to the MMC.

The sensor name in its SDR has a name prefix which after module insertion is automatically adapted to the physical position of the module in a carrier or in a  $\mu$ TCA chassis. The format of this prefix is:

- in AMC bay 1...8 or μTCA slot 1...8: 'A1:', 'A2:', 'A3:', 'A4:', 'B1:', 'B2:', 'B3:', 'B4:'.

- in µTCA slot 9...12: 'C1:', 'C2:', 'C3:', 'C4:'.

Please note that in the case that the module is installed elsewhere, then the IPMB-L address of the module is unknown and the interface is off.

Module sensors that have been implemented are listed in the sensor list below.

Table 5-1:Sensor list

| SDR<br>ID | Name          | Sensor Type Code                             | Reading Type Code         | Description                                              | Event Offset                                                                                                                                                                                                |

|-----------|---------------|----------------------------------------------|---------------------------|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0         | IPMI Info-1   | COh<br>(OEM Kontron)                         | 70h<br>(Discrete)         | Internal Management<br>Controller firmware<br>diagnostic |                                                                                                                                                                                                             |

| 1         | IPMI Info-2   | COh<br>(OEM Kontron)                         | 75h<br>(Discrete)         | Internal Management<br>Controller firmware<br>diagnostic |                                                                                                                                                                                                             |

| 2         | FRU Agent     | C5h<br>(OEM Kontron FRU<br>Info Agent State) | OAh<br>(Generic Discrete) | FRU Information<br>Agent - FRU Data<br>Error Detection   | Offset 6: transition to<br>Degraded<br>Offset 8: Install Error                                                                                                                                              |

| 3         | ModuleHotSwap | F2h<br>(Module Hot<br>Swap)                  | 6Fh<br>(Sensor Specific)  | Refer to AMC.0 specification.                            | Offset 0: Module Handle Closed Offset 1: Module Handle Opened Offset 2: Quiesced Offset 3: Backend Power Failure Offset 4: Backend Power Shutdown Refer to AMC.0 R2.0 Section 3.6.6 Module Hot Swap Sensor. |

| SDR<br>ID | Name          | Sensor Type Code                                      | Reading Type Code         | Description                                                                | Event Offset                                                                                                                                                                                         |

|-----------|---------------|-------------------------------------------------------|---------------------------|----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4         | IPMBL State   | C3h<br>(OEM Kontron)                                  | 6Fh<br>(Sensor Specific)  | For additional<br>information, refer to<br>section Kontron<br>IPMB-L Link  | Offset 2: IPMB-L disabled<br>Offset 3: IPMB-L enabled                                                                                                                                                |

| 5         | MMC Stor Err  | 28h<br>(Management<br>Subsystem<br>Health)            | 6Fh<br>(Sensor Specific)  | Generates an event<br>when a local EEPROM<br>storage error is<br>detected. | Offset 1: Controller access degraded or unavailable See IPMI v1.5 table 36.3, Sensor type code 28h for sensor definition                                                                             |

| 6         | MMC Reboot    | 24h<br>(Platform Alert)                               | 03h<br>(Digital Discrete) | Generates an event when MMC reboot is detected.                            | Offset 0: State Deasserted Offset 1: State Asserted                                                                                                                                                  |

| 7         | MMC FWUP      | C7h<br>(Kontron OEM MC<br>Firmware Upgrade<br>Status) | 6Fh<br>(Sensor Specific)  | Generates events<br>after IPMI Firmware<br>upgrade process is<br>finished  | Offset 0: Firmware upgrade in progress (no event) Offset 1: Firmware upgrade succeeded                                                                                                               |

| 8         | MMC Ver Chg   | 2Bh<br>(Version Change)                               | 6Fh<br>(Sensor Specific)  | Generates an event<br>when the IPMI FW<br>changes                          | Offset 1: Firmware / Software change detected See IPMI v1.5 table 36.3, Sensor type code 2Bh (Version Change) for sensor definition                                                                  |

| 9         | FPGA Ver Chg  | 2Bh<br>(Version Change)                               | 6Fh<br>(Sensor Specific)  | Generates an event when the IPMI FW changes                                | Offset 1: Firmware / Software change detected                                                                                                                                                        |

| 10        | IPMI Watchdog | 23h<br>(Watchdog 2)                                   | 6Fh<br>(Sensor Specific)  | OS Watchdog                                                                | Offset 0: Timer expired Offset 1: Board Reset Offset 2: Power Down Offset 3: Power Cycle Offset 8: Timer Interrupt See IPMI v1.5 table 36.3, Sensor type code 23h (Watchdog 2) for sensor definition |

| 11        | Board Reset   | CFh<br>(OEM Kontron<br>Reset Sensor)                  | 03h<br>(Digital Discrete) | Type and source of<br>Board Reset                                          | Offset 0: Warm Reset Offset 1: Cold Reset See OEM sensor table, Sensor type code CFh for sensor definition                                                                                           |

| 12        | Temp MMC      | 01h<br>(Temperature)                                  | 01h<br>(Threshold Based)  | Temperature Sensor of the outlet region                                    | Sensor is only readable when<br>Payload Power is on                                                                                                                                                  |

| 13        | Temp NPU      | 01h<br>(Temperature)                                  | 01h<br>(Threshold Based)  | Temperature Sensor of the NPU                                              | Sensor is only readable when Payload Power is on                                                                                                                                                     |